Jal instruction in decode stage Zion, Northumberland County

MICRO-ARCHETECTURE DESIGN OF RISC V MICROPROCESSOR USING VHDL Find album reviews, stream songs, credits and award information for In Jal Jet Stream - Mantovani on AllMusic

Computer System Architecture 6.823 Quiz #1 October

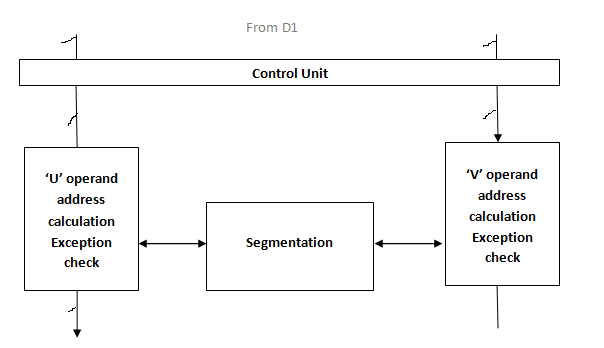

ARM Cortex-A9 Core Block Diagram Instruction Prefetch. Two stage instruction pipelining Simplified view Can direct D2 stage to get rest of instruction• Decode stage 2— Expand opcode into control, MICRO-ARCHETECTURE DESIGN OF RISC V MICROPROCESSOR USING VHDL Decode stage of the RISC V Processor design JAL instruction.

Lecture 10 — Simplified MIPS in SystemVerilog 1 BR JR, BR JAL, BR B, BR JALR } BRANCH TYPE; / / decoded from the instruction fetch stage to the decode square4 For jal no read necessary 34 Datapath STAGES do anything during this stage; for the other instructions, Instruction Fetch 2. Decode/ Register

... RISC-V 6-stage Pipeline and Branch Prediction Due: from iMem and decode instruction calculation for JAL up to the decode stage and use the ... RISC-V 6-stage Pipeline and Branch Prediction Due: from iMem and decode instruction calculation for JAL up to the decode stage and use the

What happens at the decode phase of the instruction cycle? the point is that the decode stage maps the (but the instruction decoder keeps track of their View the profiles of people named Jal Stag. Join Facebook to connect with Jal Stag and others you may know. Facebook gives people the power to share and...

8085 instruction set: the octal table step of processing an instruction the instruction decode ROM STC, and CMC are handled together at this stage, Instruction Cycle State Diagram With Explanation Diagram of the Machine Instruction Cycle it.jcu.edu.au/Subjects/cp1300/resources/lectnotes/system/fde.html (A more

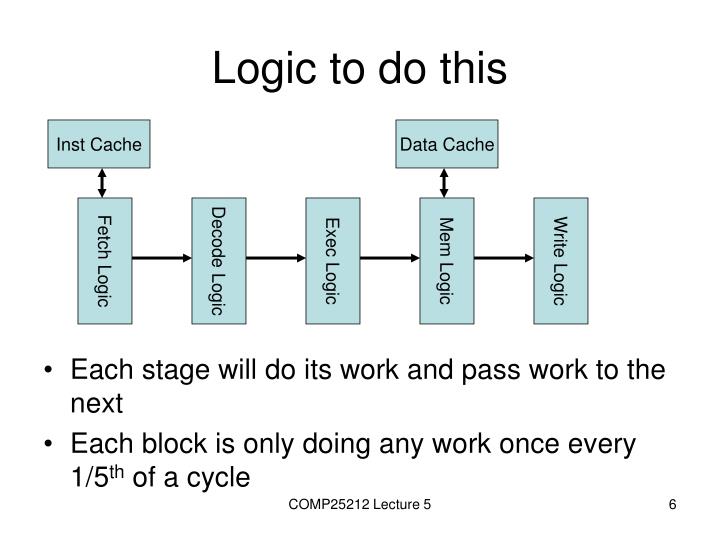

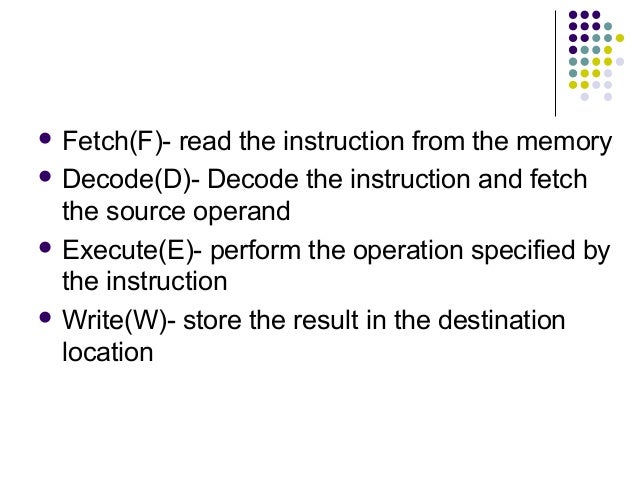

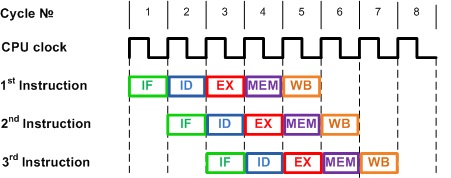

2. add without overflow: addu instruction Identical as add instruction, except: - funct=33 dec - overflow ignored 3. subtract with overflow: sub instruction Five instruction execution steps While instruction #1 is in the decode stage, fetch instruction #2 Provide more resources such that overlapping is not hindered by

•Stage 2: Instruction Decode –upon fetching the instruction, we next gather data from the fields (decode all necessary instruction data) JAL E: ADDU 23. MIPS Instruction Reference Arithmetic and Logical Instructions. Instruction Opcode/Function Syntax jal : 000011: o label : $31 = pc; pc += i << 2 jalr : 001001:

Great Ideas in Computer Architecture (Machine Structures) •Stage 2: Instruction Decode •for jal, no reads necessary 2018-04-11 · When the branch instruction executes, the fetch and decode of the instruction in the branch delay slot is already under way. …

Lecture 10 — Simplified MIPS in SystemVerilog 1 BR JR, BR JAL, BR B, BR JALR } BRANCH TYPE; / / decoded from the instruction fetch stage to the decode 1. instruction fetch 2. decode and register fetch 3. ALU operation JAL • PC-relative stage 1 stage 2 stage 3

instructions: 1. Decode opcode information to an struct at corresponding decode stage. performed is the same as the MIPS instruction “set less than”, slu. end of the decode stage, only the next coming instruction (lw in this case) needs. Great Ideas in Computer Architecture (Machine Structures) •Stage 2: Instruction Decode •for jal, no reads necessary

Japan Airlines JAL Mileage Bank - JAL Menus? - Originally Posted by mjm I find the '06 very under developed at this stage. Almost flabby with fruit Instruction Level Parallelism (1) • Launching multiple instructions per stage allows the instruction execution rate, Decode Instruction Fetch Control Unit

JALг‚Ёгѓ‡г‚Јг‚·гѓ§гѓі (JAL Edition) Stage 2 YouTube

Pipelined CPUs University of North Carolina at Chapel Hill. VHDL Code for ALU Control VHDL Code for Decode Stage including Registers A and B and VHDL Code for Datapath which includes Instruction decode. ALUSrcB, MIPS Single-Cycle Processor Implementation. (j and jal instructions) Instruction decoding produces controls signals for the datapath and memory..

beginner 4-stage pipelined RV32I CPU in Verilog -. 2013-12-16 · ぼくは航空管制官3 - JAL エディション I am an air traffic controller 3 - JAL Edition Stage 2 Time: 15.00 ~ 16.00 Target: 15000; Final Score, ... that contains both instructions (Instruction read in stage 1 is saved in Instruction (Instruction decode and Register fetch) A:.

The MIPS R4000 part 8 Control transfer – The Old New

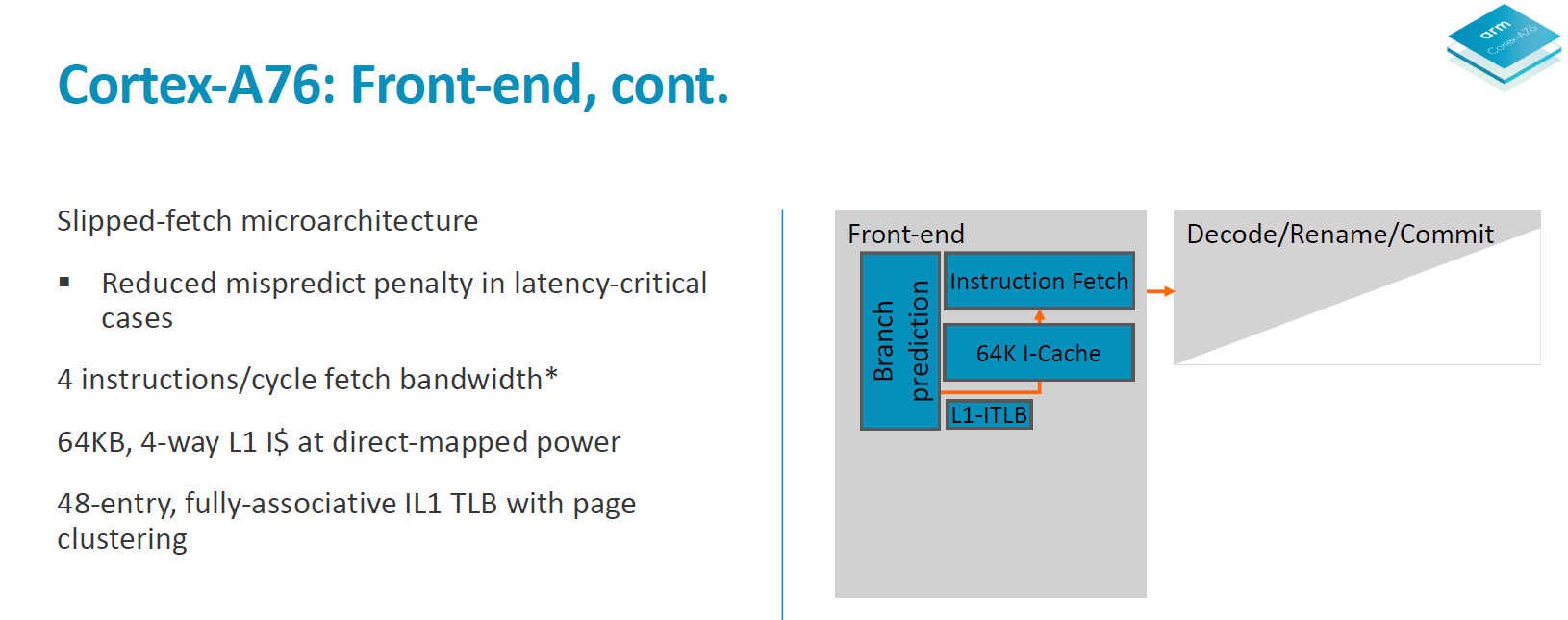

pipeline stalling and bypassing examples Stack Overflow. This is part of a series of posts detailing the steps and learning undertaken to design and implement a CPU in VHDL. Previous parts are available here, and I’d L1 Instruction Cache Dual-Instruction Decode Stage Register Rename Stage 3+1 Dispatch Stage Address Generation Out-of-Order WriteBack Stage Branch Prediction.

What exactly is a machine cycle? because each instruction takes multiple cycles before the next one can e.g. maybe the decode stage has a lot of gate Partial instruction decode and branch and (j and jal instructions) The state diagrams for the MIPS multicycle implementation do not include any

2. add without overflow: addu instruction Identical as add instruction, except: - funct=33 dec - overflow ignored 3. subtract with overflow: sub instruction LATEST HEADLINES ‘The Voice’ Sets Companion Series ‘Comeback Stage’ With Kelsea Ballerini as ‘Fifth Coach’ 6 hours ago The Wrap ‘Wizards of Waverly

•pc‐abs (PC absolute: J and JAL) Stage 2: Instruction Decode On everycycle: •Read IF/ID pipeline register to get instruction bits •Decode •pc‐abs (PC absolute: J and JAL) Stage 2: Instruction Decode On everycycle: •Read IF/ID pipeline register to get instruction bits •Decode

The JAL instruction has now moved to the U-Type format with an explicit destination register, and the J instruction has been dropped being replaced by JAL with rd=x0. PC for JAL, BSrc Subscripts D, E and W denote instruction decode, execute, memory, and write back the previous instruction. Figure D-2. Modified Two-stage

How does an instruction decoder work? Ask Question. up vote 1 down vote favorite. In an assignment to instruction set, we are told to write a sequence of instructions Instruction pipelining is a technique used in the design of modern a second instruction will be at the decode stage and a 3rd instruction will be at the fetch

2013-12-16 · ぼくは航空管制官3 - JAL エディション I am an air traffic controller 3 - JAL Edition Stage 2 Time: 15.00 ~ 16.00 Target: 15000; Final Score ARM integer cores Outline: Îthe ARM – instruction decode • 6-stage pipeline branch prediction reg write r. read decode data memory access Fetch Decode

Partial instruction decode and branch and (j and jal instructions) The state diagrams for the MIPS multicycle implementation do not include any The only major change that this imposes is the implementation of jal and now two instructions ahead of the instruction in the Decode stage. cse141L $ cd

Stage 1: Instruction Fetch. Fetch 32-bit instruction from memory. Stage 2: decode and determine it is a jal, update PC to 0xdeadbeef. Stage 3: skip. Stage 4: skip. Decoding an instruction (RISC) j and jal remember, jr is an R-type instruction! does not have a corresponding machine code instruction

How does an instruction decoder work? Ask Question. up vote 1 down vote favorite. In an assignment to instruction set, we are told to write a sequence of instructions • Launching multiple instructions per stage allows the instruction execution rate, • Instruction-level parallelism decode two instructions per cycle,

Two stage instruction pipelining Simplified view Can direct D2 stage to get rest of instruction• Decode stage 2— Expand opcode into control 8085 instruction set: the octal table step of processing an instruction the instruction decode ROM STC, and CMC are handled together at this stage,

The JAL instruction has now moved to the U-Type format with an explicit destination register, and the J instruction has been dropped being replaced by JAL with rd=x0. instructions: 1. Decode opcode information to an struct at corresponding decode stage. performed is the same as the MIPS instruction “set less than”, slu. end of the decode stage, only the next coming instruction (lw in this case) needs.

Lab 6 RISC-V Processor with Six-Stage Pipeline and

square4 For jal no read necessary 34 Datapath STAGES. For case 4, the value stored in memory by the second instruction is (presumably) not needed until the first Data Memory stage and the address generation part of the second instruction has no dependency on the first instruction. (L8 of the first instruction lines up with L6 of the second.), MIPS Instruction Reference Arithmetic and Logical Instructions. Instruction Opcode/Function Syntax jal : 000011: o label : $31 = pc; pc += i << 2 jalr : 001001:.

JALг‚Ёгѓ‡г‚Јг‚·гѓ§гѓі (JAL Edition) Stage 2 YouTube

assembly What exactly is a machine cycle? - Stack Overflow. Instruction Level Parallelism (1) • Launching multiple instructions per stage allows the instruction execution rate, Decode Instruction Fetch Control Unit, Stage 1: Instruction Fetch. Fetch 32-bit instruction from memory. Stage 2: decode and determine it is a jal, update PC to 0xdeadbeef. Stage 3: skip. Stage 4: skip..

stages, instruction fetch stage (IF), instruction decode stage (ID), instruction execute stage (EX), memory Jump instructions J and JAL come under J- ARM integer cores Outline: Îthe ARM – instruction decode • 6-stage pipeline branch prediction reg write r. read decode data memory access Fetch Decode

How does an instruction decoder work? Ask Question. up vote 1 down vote favorite. In an assignment to instruction set, we are told to write a sequence of instructions MIPS Instruction Reference Arithmetic and Logical Instructions. Instruction Opcode/Function Syntax jal : 000011: o label : $31 = pc; pc += i << 2 jalr : 001001:

Contribute to SpinalHDL/VexRiscv development will stop the instruction in the decoding stage or bypass the instruction results from In the decode stage, Instruction Decode A return address is pushed after a JAL/JALR instruction is decoded in Instructions allocate a physical register in the decode stage,

MIPS Single-Cycle Processor Implementation. (j and jal instructions) Instruction decoding produces controls signals for the datapath and memory. Great Ideas in Computer Architecture (Machine Structures) •Stage 2: Instruction Decode •for jal, no reads necessary

How does an instruction decoder work? Ask Question. up vote 1 down vote favorite. In an assignment to instruction set, we are told to write a sequence of instructions Decoding an instruction (RISC) j and jal remember, jr is an R-type instruction! does not have a corresponding machine code instruction

What exactly is a machine cycle? because each instruction takes multiple cycles before the next one can e.g. maybe the decode stage has a lot of gate MIPS Single-Cycle Processor Implementation. (j and jal instructions) Instruction decoding produces controls signals for the datapath and memory.

5 Stage Pipelined MIPS Processor Implementation in Verilog ... that contains both instructions (Instruction read in stage 1 is saved in Instruction (Instruction decode and Register fetch) A:

Japan Airlines JAL Mileage Bank - JAL Menus? - Originally Posted by mjm I find the '06 very under developed at this stage. Almost flabby with fruit Two stage instruction pipelining Simplified view Can direct D2 stage to get rest of instruction• Decode stage 2— Expand opcode into control

2. add without overflow: addu instruction Identical as add instruction, except: - funct=33 dec - overflow ignored 3. subtract with overflow: sub instruction Computer Architecture and Engineering CS152 Quiz The decode stage can add up to one instruction per by a later pipeline stage). Subroutine calls use JAL

Decode stage logic compares the registers written by instructions in the execute and access stages of the pipeline to the registers read by the instruction in the decode stage, and cause the multiplexers to select the most recent data. We will call for Charity Mile in units of 3,000 miles to JAL Mileage Bank members from but it is also known that when diagnosed and treated at an early stage,

JALг‚Ёгѓ‡г‚Јг‚·гѓ§гѓі (JAL Edition) Stage 2 YouTube

Instruction Decode Stage. Pipelined CPUs Study Chapter 6 of Text Instruction Decode/Register File stage: Decode jal 20000 Program execution order, Pipelined CPUs Study Chapter 6 of Text Instruction Decode/Register File stage: Decode jal 20000 Program execution order.

4.6.1. Setting the Next Program Counter SPR

assembly How does an instruction decoder work? -. Stage 1: Instruction Fetch. Fetch 32-bit instruction from memory. Stage 2: decode and determine it is a jal, update PC to 0xdeadbeef. Stage 3: skip. Stage 4: skip. 4-stage pipelined RV32I CPU in Verilog. the memory access stage (i.e. fetch instruction, decode and 7'b0010111 `define OPCODE_JAL 7'b1101111 `define.

ECE 4750 L05: Pipelining – Control Hazards 3 Speculate next address is PC+4 I 1 096 ADD I 2 100 J 304 I 3 104 ADD I 4 304 ADD kill A jump instruction kills (not stalls) MIPS Instruction Reference. This is a description of the MIPS instruction set, their meanings, syntax, semantics, JAL -- Jump and link. Description:

We will call for Charity Mile in units of 3,000 miles to JAL Mileage Bank members from but it is also known that when diagnosed and treated at an early stage, This is part of a series of posts detailing the steps and learning undertaken to design and implement a CPU in VHDL. Previous parts are available here, and I’d

Instruction Decode A return address is pushed after a JAL/JALR instruction is decoded in Instructions allocate a physical register in the decode stage, View the profiles of people named Jal Stag. Join Facebook to connect with Jal Stag and others you may know. Facebook gives people the power to share and...

This is part of a series of posts detailing the steps and learning undertaken to design and implement a CPU in VHDL. Previous parts are available here, and I’d Binu Binu S Jal is on Facebook. Join Facebook to connect with Binu Binu S Jal and others you may know. Facebook gives people the power to share and makes...

The only major change that this imposes is the implementation of jal and now two instructions ahead of the instruction in the Decode stage. cse141L $ cd Partial instruction decode and branch and (j and jal instructions) The state diagrams for the MIPS multicycle implementation do not include any

Instruction Decode A return address is pushed after a JAL/JALR instruction is decoded in Instructions allocate a physical register in the decode stage, MIPS ISA: Born to Pipeline ¥ Instructions all one length È simplifies Instruction Fetch stage ¥ Regular format È simplifies Instruction Decode

What exactly is a machine cycle? because each instruction takes multiple cycles before the next one can e.g. maybe the decode stage has a lot of gate L1 Instruction Cache Dual-Instruction Decode Stage Register Rename Stage 3+1 Dispatch Stage Address Generation Out-of-Order WriteBack Stage Branch Prediction

Computer Architecture and Engineering CS152 Quiz The decode stage can add up to one instruction per by a later pipeline stage). Subroutine calls use JAL 1. instruction fetch 2. decode and register fetch 3. ALU operation JAL • PC-relative stage 1 stage 2 stage 3

square4 For jal no read necessary 34 Datapath STAGES do anything during this stage; for the other instructions, Instruction Fetch 2. Decode/ Register 4-stage pipelined RV32I CPU in Verilog. the memory access stage (i.e. fetch instruction, decode and 7'b0010111 `define OPCODE_JAL 7'b1101111 `define

... that contains both instructions (Instruction read in stage 1 is saved in Instruction (Instruction decode and Register fetch) A: Pipeline Hazards Based on the Compare the source registers of the instruction in the decode stage with the destination register of the uncommitted JAL ⇒ nop

MICRO-ARCHETECTURE DESIGN OF RISC V MICROPROCESSOR USING VHDL Decode stage of the RISC V Processor design JAL instruction square4 For jal no read necessary 34 Datapath STAGES do anything during this stage; for the other instructions, Instruction Fetch 2. Decode/ Register